When designers look to move up in abstraction from RTL to C/SystemC one of the first questions that they ask is; “what does my verification methodology look like?”. In RTL, methodologies for verification are known and proven, but when using High-Level Synthesis (HLS), the same ecosystem is not established across the industry. This session highlights proven tools and methodology that help an HLS designer check and verify his design, measure, and close coverage, and compare the C to RTL implementation. Resulting in enabled verification at the C++ level with all of the same methodologies deployed at RTL.

This webinar is part 3 of the seminar Rapid Algorithm to HW: Using HLS for Computer Vision and Deep Learning.

What you will learn:

- How HLS can be used to implement an example Computer Vision

Algorithm in either an FPGA or ASIC technology and the trade-offs for

power and performance. You will walk away with examples, building

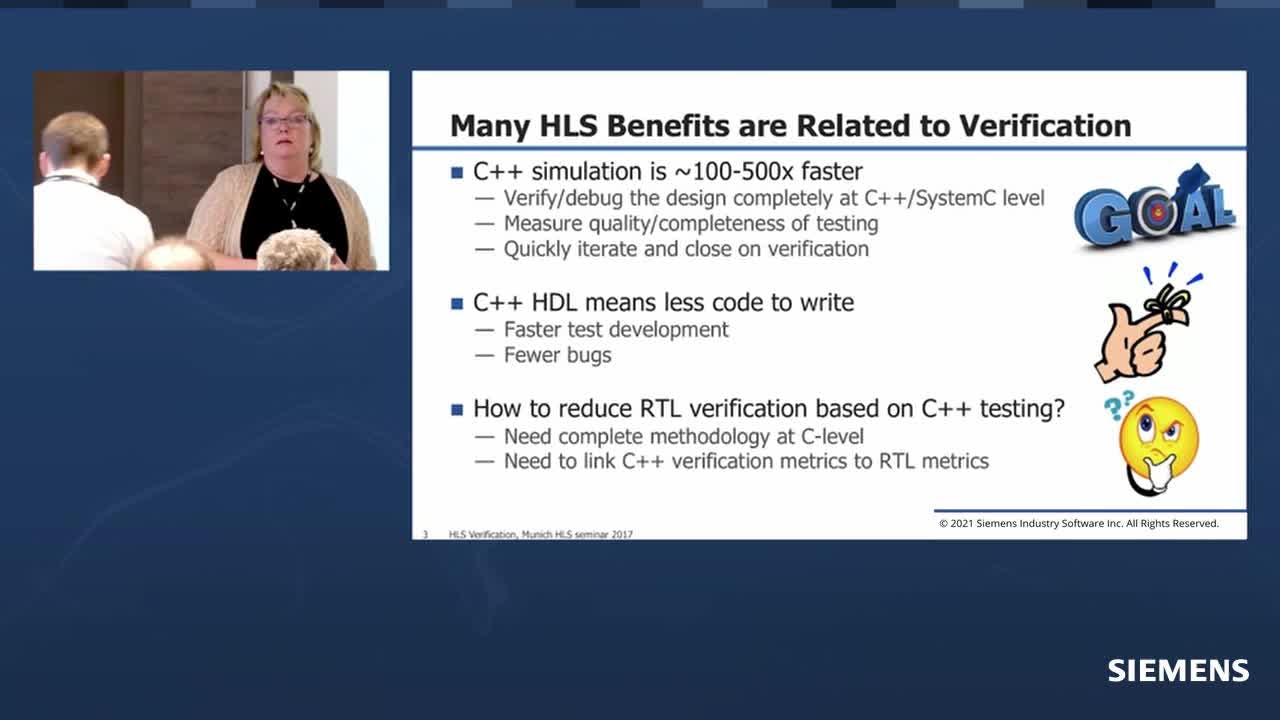

blocks, etc that are completed and can be referenced. - How to achieve faster but complete verification signoff in an HLS

flow measuring quality, coverage; saving days and weeks in

verification costs - How HLS can be applied in multiple ways to implement acceleration

for Deep Learning and in particular Convolutional Neural Networks. You

will walk away with examples, building blocks, etc that are completed

and can be referenced.

Who should view:

- RTL Designers or Project Managers interested in moving up to HLS

- Architects or Algorithm developers in the field of image processing,

computer vision, machine and deep learning interested in rapid and

accurate exploration of power/performance metrics - New Project teams with only a few designers and multiple SW experts

wanting to rapidly create high-performance FPGA or ASIC IP for

Computer Vision or Deep Learning markets

主讲嘉宾简介

Ellie Burns

Former Director of Marketing

Ms. Burns has over 30 years of experience in the chip design and the EDA industries in various roles of engineering, applications engineering, technical marketing and product management. She was formerly the Director of Marketing for the Calypto Systems' Division at Siemens EDA responsible for low-power RTL solutions with PowerPro and HLS Solutions with Catapult. Prior to Siemens and Mentor, Ms. Burns held engineering and marketing positions at CoWare, Cadence, Synopsys, Viewlogic, Computervision and Intel. She holds a BSCpE from Oregon State University.