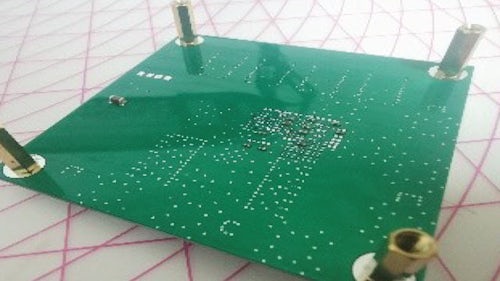

Supply chain disruptions are wreaking havoc throughout the electronics industry today. From component issues to cost increases, it’s becoming more difficult for project engineering teams to design and bring products to market on time and within budget. Functional silos, disparate systems, and fragmented cross-functional decision-making processes throughout organizations add even more complexity to the electronics supply chain problem.

Watch this webinar to learn about our three-phased approach that can create supply chain resilience at the point of design. Particular attention will be paid to the digital transformation of a shift-left or outside in approach in a workflow that today is inherently siloed, disconnected, and inefficient.

Learn more about Electronics Systems Design Supply Chain Resilience.

Meet the speaker

Stephen V. Chavez

Technical Product Manager

Stephen Chavez is a senior printed circuit engineer with three decades’ experience. He spent the past 12 years as a Principal Engineer and global subject matter expert of PCB design for Collins Aerospace (Raytheon Technologies).

Now, in his current role as a Senior Product Marketing Manager with Siemens, his focus is on a global scale regarding methodologies on adopting a strategy for resilience and integrating the Design-to-Source Intelligence insights from Supplyframe into design for resilience. He is an IPC Certified Master Instructor Trainer (MIT) for PCB design, an IPC Certified Advanced PCB Designer (CID+), and a Certified Printed Circuit Designer (CPCD). He is chairman of the Printed Circuit Engineering Association (PCEA) where his focus is on the continuous improvement, professional development, and the evolution of the printed circuit engineer throughout the industry. An active IPC member since 2003, he is currently involved in several subcommittees including specifications IPC-6012, IPC-2221/2222.

Chavez is recognized as an industry subject matter expert in PCB design by PCEA, IPC, and several leading industry publications.