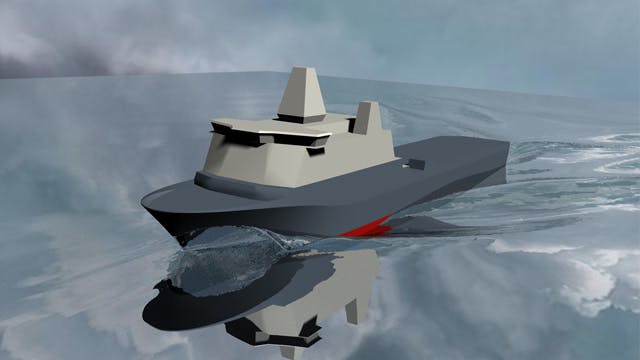

Computational fluid dynamics (CFD), especially hydrodynamic simulation, is key to meeting vessel design targets and predicting realistic performance in complex operating scenarios. However, simulation times can be long, due to the size of models and the complexity of physics required. In this on-demand webinar, learn how the latest advances in marine CFD technology can help you rapidly analyze complex scenarios and explore alternative vessel designs.

How to streamline the shipbuilding design process?

New developments in engineering simulation are making it possible to see huge gains in productivity that can streamline the shipbuilding design process. Things like the multi-mesh sequencing method and adaptive mesh refinement, combined with advanced multi-physics and motion models, can help take the manual work out of CFD simulation and speed up the shipbuilding design process.

Leveraging CFD simulation software for increased productivity

Frustrated by long simulation set-up and run times? You don’t need to be. Advances in CFD simulation software, such as faster meshing methods and automated design sweeps, can be applied to your CFD process to drastically reduce simulation times. Doing so allows you to see strong productivity gains.

Test high fidelity vessel designs using batch simulation

Using templates can drastically reduce setup time from hours to minutes. This also enables you to do batch simulation to test different vessel designs with high fidelity. In the webinar, you will see multiple examples of this in action using Simcenter STAR-CCM+.

Watch the webinar now to learn more.