If you missed the Maxlinear presentation at the 2023 User2User symposium about the Siemens' place and route solution, you can now access this recorded session on demand.

In this digital IC design implementation session, Ravi Ranjan, Director of Physical Design at Maxlinear, presents “How to achieve optimal PPA at placement and carry it through to signoff” using Aprisa digital implementation.

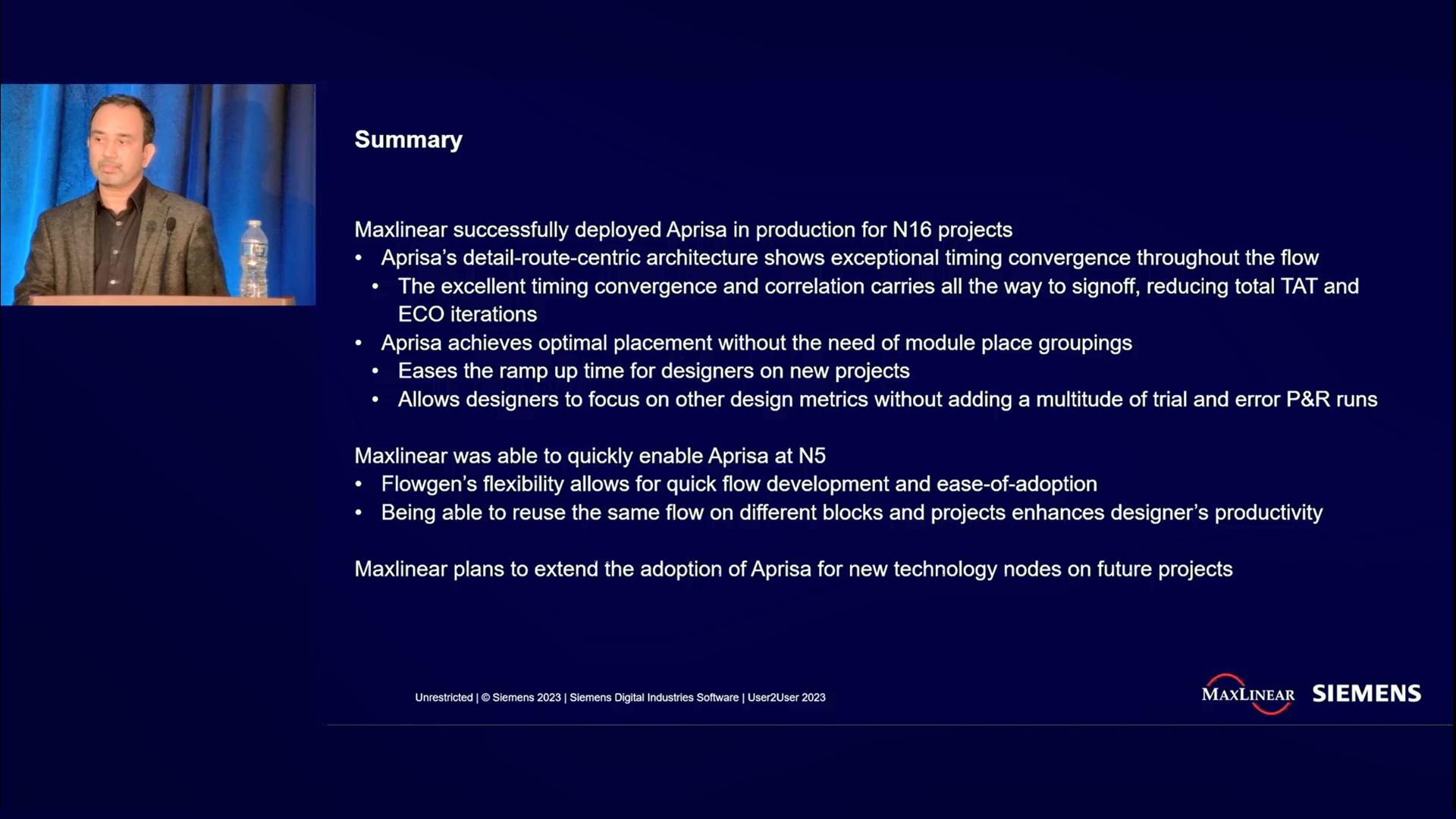

Maxlinear met aggressive performance, power and closure challenges with Aprisa

Maxlinear is a leading semiconductor supplier for broadband, connectivity, and infrastructure markets. Their products make multi-gig connectivity a reality through digital, high-performance analog and mixed-signal integrated circuits and software solutions.

In this presentation, Ravi walks us through how Maxlinear was able to meet their performance, power and closure challenges with Aprisa on a high-speed 16 nm design, and seamlessly move their existing 16 nm flow to 5 nm, experiencing for themselves, Aprisa’s correlation advantage, ease of adoption, and use.

You will learn how Maxlinear:

- Optimized and deployed their IC designs using the same flow for all blocks at different frequencies and nodes

- Enhanced their designers’ productivity when setting up their projects by using Aprisa’s flow generator FlowGen

- Achieved great QoR without the need for place guides

- Matched signoff timing without the need for margins or additional derates

- Reduced ECO cycles from weeks to days due to Aprisa’s excellent timing correlation with STA

To learn more about how Aprisa delivers complete functionality for top-level hierarchical design and block-level implementation for complex digital IC designs visit our web page.

Poznaj naszego eksperta

Ravi Ranjan

Director, Physical Design