The following 9-part video series provides a step-by-step walkthrough of what is needed to take a C++ floating-point algorithm all the way to optimized RTL using Catapult High-Level Synthesis.

Video 0: Floating point C++ Algorithm to Optimized RTL Implementation Using Catapult High Level Synthesis

This video provides an introduction to the Edge Detection video series and an overview of the Catapult HLS flow.

Video 1: Going From Algorithm to Optimized Implementation Using High-Level Synthesis (HLS)

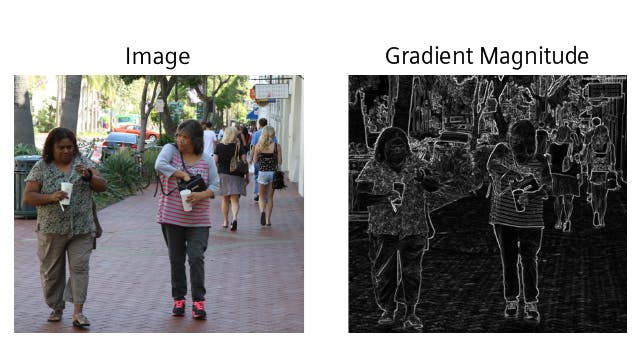

This video provides an overview of the edge detection image processing algorithm used for all of the design walkthroughs in this video series.

Video 2: Using Bit Accurate Datatypes

In this video the edge detection algorithm is converted to use bit-accurate data types.

Video 3: Making the C++ Synthesizable

In this video the bit-accurate model is modified so that it is synthesizable by Catapult. Catapult is then used to optimize the design and analyze performance bottlenecks.

Video 4: Sliding Window Memory Architecture for Performance

In this video the design is recoded to improve performance by adding a sliding window memory architecture. Automated verification is then run on the design and test bench.

Video 5: Multi-block Concurrency for Highest Performance

In this video the design is recoded to further improve performance by coding each design class so that it will be synthesized as a separate concurrent process.

Video 6: Converting from Dual Port to Single Port Memory

This video shows how to recode the C++ so that only single port memories are required to achieve the performance requirements.

Video 7: Making the Hardware Configurable

In this video the C++ is modified to make the synthesized hardware reconfigurable.

Video 8: Circular Buffer Memory Architecture for Reducing Power

This video recodes the C++ to use a circular buffer memory architecture and demonstrates the Catapult power analysis flow.

Video Modules Overview

The video modules are broken down into the following nine categories: We start first with a basic overview of the Catapult flow using a simple design. Module 1 provides an overview of the edge detection algorithm. In module 2 we convert the floating-point algorithm to use bit-accurate data types. Module 3 then makes the algorithm synthesizable. Module 4 uses a sliding window memory architecture in order to improve performance. In module 5 we add multi-block concurrency to achieve the highest performance. Module 6 consists of converting from a dual port to a single port memory architecture. Module 7 involves making the hardware more configurable. In module 8 we finish up by converting the memory architecture to use a circular buffer memory architecture to reduce power.

If you would like to step through this design you can do so by downloading this file here.

발표자 소개

.jpg?auto=format,compress)

Michael Fingeroff

HLS Technologist

Michael Fingeroff has worked as an HLS Technologist for the Catapult High-Level Synthesis Platform at Siemens Digital Industries Software since 2002. His areas of interest include Machine Learning, DSP, and high-performance video hardware. Prior to working for Siemens Digital Industries Software, he worked as a hardware design engineer developing real-time broadband video systems. Mike Fingeroff received both his bachelor's and master's degrees in electrical engineering from Temple University in 1990 and 1995 respectively.