In theory, there is no difference between theory and practice but in practice there is. This saying holds great value during Silicon bring-up stage in the semiconductor industry. There is a sea of difference in how product engineering executes test on ATE and how it is envisaged by the DFT engineer. The gulf between the two roles has many loopholes and can result in inefficient execution followed by missing the all-important product window.

The path to better silicon bring-up

In theory, there is no difference between theory and practice but in practice there is. This saying holds great value during the silicon bring-up stage in the semiconductor industry. There is a sea of difference in how product engineering executes test on ATE and how it is envisaged by the DFT engineer. The gulf between the two roles has many loopholes and can result in inefficient execution followed by missing the all-important product window.

In this regard, there are several logistical and technical problems that create challenges:

- Adherence to proprietary tester protocols and collateral

- Limited or reserved time slots allocated on ATE

- Cross functional operations between the test/product engineers and design

- Longer TAT for diagnosing & root cause of failures in silicon

- Lack of resolution while reverse mapping the chip level failure data

In addition to above mentioned parameters, performance characterization of silicon is vital for rapid yield ramp-up and improved time to market.

Key takeaways for you from this session:

- How key silicon bring-up challenges for IJTAG/MBIST/EDT/LBIST are addressed?

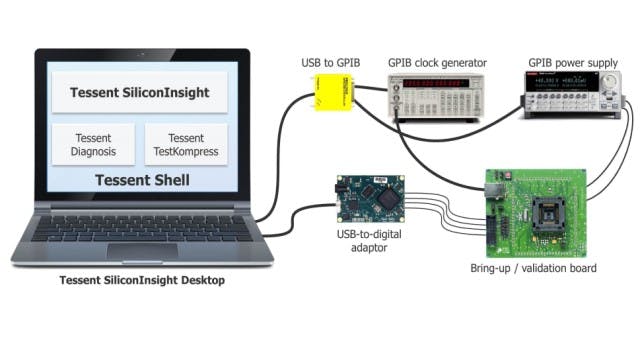

- How schedule curve can be met with the help of Tessent SiliconInsight?

- How efficient characterization can be performed on new silicon and field return parts

Who can benefit from the webinar:

- Design for test engineers, managers and directors

- IC design engineers/managers

- CAD engineers

- Product & operations teams

Meet the speaker

Kaushik Jammy

Corporate Application Engineer - DFT

Kaushik is a Corporate Application Engineer working in DFT profile for Siemens EDA, India. Kaushik supports customers in MBIST and SiliconInsight domains. He holds a Masters degree in VLSI from Vellore Institute of Technology.