Kontinuierliche Qualitätsverbesserungen und die Reduzierung von Frühausfällen sind wichtige Ziele für Halbleiterhersteller und ihre Kunden. Zu den sensibelsten Anwendungen gehören die Elektrifizierung von Fahrzeugen, Server, Militär und Verteidigung sowie Konsumgüter.

In der Vergangenheit haben Halbleiterunternehmen mit elektrischen Tests oder raumbezogenen Verfahren frühzeitig zur Reduzierung von Ausfällen über die gesamte Lebensdauer hinweg Maßnahmen ergriffen, um potenzielle Ausfälle auszuschließen oder zu testen. Burn-in-Verfahren und prädiktive Testmethoden wie die Durchschnittsprüfung von Teilen gibt es schon lange. Darüber hinaus werden andere raumbezogene Methoden wie visuelles Defekt-Screening und algorithmisches Ertrags-Clustering für die Ermittlung abnormaler Muster verwendet, um frühe Ausfälle im Lebenszyklus vorherzusagen.

Bedeutung thermischer Prüfungen bei der Halbleiterentwicklung

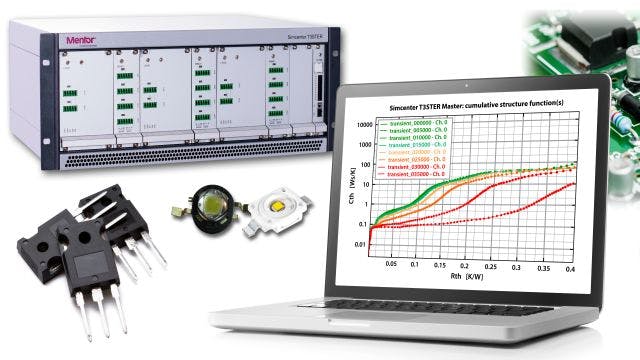

Im heutigen Streben nach Null-Fehlern und besserer Nachhaltigkeit müssen Unternehmen Fertigungsfehler und Variabilität reduzieren. Inline-Messungen des Wärmewiderstands sind ein weiterer Weg zur Qualitätsoptimierung in Halbleiterunternehmen. Thermisch-transiente Testmethoden können die Temperaturreaktionen von Halbleiterdiaphragma auf kurze Pulse messen und Einblicke in potenzielle Fertigungsfehler geben. Die Technologie kann Inkonsistenzen im Wärmeleitungspfad aufdecken, ihren Einfluss auf den Wärmewiderstand quantifizieren und ihre Position hervorheben. Probleme wie Wärmeleitmaterial (TIM1) oder Die-Attach-Voids oder Delamination lassen sich in Sekundenbruchteilen lokalisieren, aber auch Probleme außerhalb des Gehäuses, wie z. B. die TIM2-Qualität, können mit kurzen Impulsen gemessen werden.

In diesem Webinar erfahren Sie, wie sich Temperaturänderungen in Halbleitergehäusen mit thermisch-transienten Testmethoden messen und potenzielle Fertigungsfehler identifizieren lassen.

Lernen Sie in diesem Webinar hoch entwickelte thermische Prüfungen und Die-Attach-Techniken kennen

Sie sehen in diesem Webinar:

- die Rolle thermisch-transienter Testmethoden zur Unterstützung der Analyse von Gehäusemodellen

- Anwendung von Strukturfunktionen zur Fehleridentifikation

- Testen von Anwendungsfällen und Grenzwerten für die thermische Qualität von Gehäusen

- verschiedene Möglichkeiten, ein Testsystem in eine Halbleiterproduktionsumgebung zu integrieren

Vorstellung des Referenten

Andras Vass-Varnai

Portfolio Development Executive for Electronics and Semiconductor

Andras Vass-Varnai erwarb seinen Master- und Doktor-Abschluss in Elektrotechnik an der Technischen und Wirtschaftswissenschaftlichen Universität Budapest. Seine berufliche Laufbahn begann er 2007 bei der MicReD-Gruppe von Mentor Graphics als Anwendungsingenieur. Andras war über 10 Jahre lang hauptsächlich als Produktmanager tätig und unterstützte Entwicklungsprojekte, wie z. B. die DynTIM- oder Powertester-Geräte. Bevor er seine jetzige Rolle als Portfolioentwicklungsleiter für den Elektronik- und Halbleitermarkt bei Siemens antrat, arbeitete Andras von Seoul, Korea, aus, wo er die asiatischen Geschäftsaktivitäten unterstützte. Derzeit arbeitet er von Chicago, Illinois, aus und konzentriert sich auf den Ausbau des US-Geschäfts. Zu seinen Fachgebieten gehören das Wärmemanagement elektrischer Systeme, fortgeschrittene Anwendungen der thermisch-transienten Prüfung und Modellierung, die Charakterisierung von TIM-Materialien und die Zuverlässigkeitsprüfung von leistungsstarken Halbleiterbauelementen.